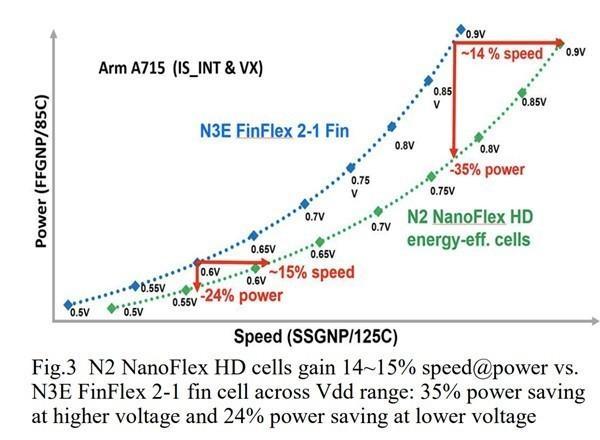

台积电最近在IEEE国际电子设备会议上首次公布了其2nm工艺的详细技术指标和未来应用前景。根据介绍,台积电2nm工艺相较于目前商用的3nm工艺,有着显著的性能提升及更低的功耗。在相同功耗下,性能提升可达15%,而在同等性能下,功耗将降低24%至35%。这一关键技术指标使得2nm工艺在高性能AI芯片领域极具吸引力。

台积电2nm工艺采用了全新的GAA(Gate-All-Around)纳米片晶体管技术。这种晶体管技术通过垂直排列的水平纳米片在四个侧面包围通道,从而优化了电流控制机制,降低了漏电率并增强了驱动电流。相较于前代的FinFET晶体管,GAA技术在低电压下能效显著提升,频率可提高约20%,待机功耗则降低约75%。

此外,台积电引入了NanoFlex DTCO(设计技术协同优化)技术,这一技术允许设计人员调整通道宽度,从而在性能与能效之间实现平衡。NanoFlex DTCO使得N型和P型纳米片晶体管的I/CV速度分别提升了70%和110%。同时,SRAM密度也创下新高,达到每平方毫米约38Mb,大大提升了芯片的性能和能效指标。

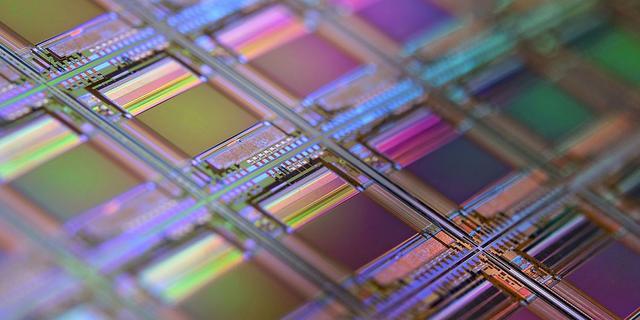

台积电2nm工艺的良品率在试生产阶段已经超过60%,高于预期水平。这一高良品率为2025年的量产计划奠定了基础。去年,台积电董事长兼首席执行官魏哲家指出,未来五年台积电有望实现连续、健康的增长,尤其在AI芯片领域,客户对2nm工艺需求强劲,市场前景广阔。魏哲家还表示,客户对于2nm的询问多于3nm,这说明2nm工艺受到了更多客户的青睐。

台积电的2nm工艺不仅在单晶体管密度和功耗方面有显著提升,在制造工艺上也有诸多创新。例如,全新的MOL中段工艺和BEOL后段工艺大大降低了电阻提升了能效。中间层的钨导线设计及其减少55%的垂直接触电阻,让振荡器频率提高了约6.2%。第一金属层(M1)的1P1E(一次蚀刻和一次EUV曝光)处理方式简化了工艺步骤并提高了整体工艺的效率。

在芯片封装方面,台积电的深耕也颇有成效,尤其是CoWos封装技术。该技术将多个关键芯片高度集成到一个封装体内,包括处理器、内存等功能模块,从而实现更高密度的系统集成。这种封装技术在AI芯片领域尤其关键,将成为先进工艺特性的重要补充。

2nm工艺的成本问题无疑是一个重要关注点。预计每片300mm的2nm晶圆价格会超越3万美元,高于3nm芯圆的价格。这一显著的价格提升也引发了市场对其经济效益的讨论。然而,台积电通过持续的投资和扩展产能规划,计划在未来几年内提高2nm工艺的生产效率并降低成本。

此外,台积电与Amkor在芯片生产、封装和测试上的合作也将进一步提升2nm工艺的生产能力和效率。亚利桑那州的合作工厂将缩短芯片生产周期,提高整体生产效益,这是台积电应对全球半导体市场竞争的战略举措。

在实际应用方面,苹果预计将成为台积电2nm工艺的首批用户。苹果的iPhone 18 Pro有望搭载这一先进芯片,从而在性能和能效上实现跨越式提升。预计与2nm工艺相关的技术和产品将在2026年得到广泛应用,进一步推动智能手机和PC市场的发展。

台积电2nm工艺在AI芯片中前景广阔。其性能和能效显著提升,以及良品率高和制造工艺的创新,让2nm工艺在高性能计算和移动设备申请中充满潜力。同时,尽管面临成本和能源消耗的挑战,台积电通过持续投资和技术创新有望稳步推进新工艺的量产与应用。这些进展不仅巩固了台积电在半导体制造领域的领先地位,也为未来半导体技术的发展提供了新的可能性。

本文来自:什么值得买