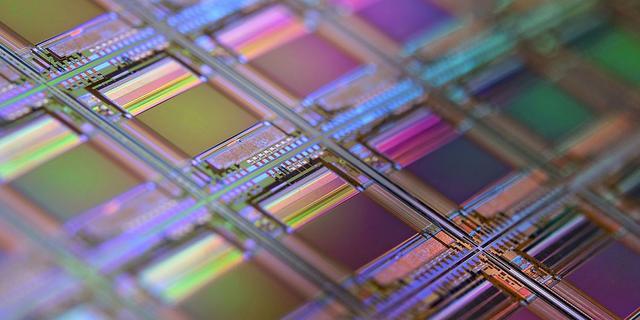

台积电作为全球顶尖的晶圆代工厂,近年来在制程工艺上不断突破,引发了业界的广泛关注。尤其是台积电2nm技术相较于3nm技术的显著进步,标志着半导体制造技术的又一次飞跃。在探讨这一转变时,我们将详细分析台积电2nm技术相较于3nm技术的关键区别,具体包括晶体管架构、功耗和性能提升、新工艺的引入,以及市场影响。

台积电2nm技术的核心在于全新的晶体管架构——全环绕栅极(GAA)纳米片晶体管。这种架构不同于3nm制程采用的FinFET(鳍式场效应晶体管)技术。GAA纳米片晶体管通过围绕四个侧面的栅极实现更有效的电流控制,相比三面覆盖的FinFET晶体管,它能够极大降低漏电现象,提高驱动电流,使得晶体管在低电压下运行更高效。资料显示,台积电2nm纳米片晶体管在0.5V至0.6V的电压下,能效显著提升,待机功耗降低约75%,频率还可提高20%左右。这些改进为高性能计算和低功耗需求的应用提供了更好的技术保障。

在晶体管密度方面,台积电2nm制程相较于3nm有了明显的提升。据悉,2nm工艺的晶体管密度提高了15%,这意味着在同样大小的芯片上可以集成更多的晶体管,从而提升整体性能和处理能力。在性能和功耗方面,2nm技术同样表现出色。相同功耗下性能提高15%,而在相同性能下功耗降低24%-35%。这样的提升对当今追求高性能与能效平衡的半导体市场至关重要,特别是在移动设备和高性能计算领域,能够为用户提供更长的电池续航时间以及更强的计算能力。

第三,台积电2nm技术引入了许多新的工艺和材料改进。例如,NanoFlex DTCO(设计技术协同优化)的应用,可以开发更小面积但能效更高或性能更强的单元,旨在优化芯片设计和制造流程。NanoFlex DTCO提供了设计上的灵活性,使得芯片设计师能够在不同的应用场景下调整逻辑单元的表现。此外,台积电还在2nm工艺中采用了新型的MOL(中层工艺)和BEOL(后工程工艺),其电阻降低了20%,进一步提升了能效。同时,台积电的新工艺支持第一层金属层(M1)通过一步蚀刻(1P1E)和一次极紫外(EUV)曝光完成,极大简化了工艺的复杂性和光罩的数量,从而降低了制造成本和时间。

此外,2nm制程中引入的第三代偶极子技术,包括N型和P型晶体管对应的不同电压阈值,支持六个电压阈值档,范围在200mV。这项改进使N型和P型纳米片晶体管的I/CV速度分别提升了70%和110%。新电路架构使得在不同性能需求下都能够达到最佳的性能与功耗平衡,也为芯片设计的多样性提供了广泛的支持。

谈到市场影响,台积电显然意识到了2nm技术对未来市场的重要性。据报道,台积电计划在2025年下半年实现2nm技术的量产。为了实现这一目标,台积电正在加速建设新的生产线,并不断扩大产能规划。台积电高层表示,客户对于2nm技术的兴趣超过了3nm,这一点在市场需求上得到了进一步印证。例如,苹果预计将成为台积电2nm技术的首批客户,计划将2nm工艺应用于未来的M5芯片和iPhone设备上。

不仅如此,台积电的2nm技术在财务上也将带来显著变化。尽管2nm晶圆的价格较3nm有显著上升,预计每片晶圆价格将超过3万美元,但其性能和能效提升所带来的市场价值无疑也是巨大的。随着制程技术的不断进步,先进工艺节点的研发成本和市场竞争力成为了关注焦点。台积电持续投入巨额资金用于研发和生产线扩建,以确保在全球半导体市场中保持领先地位。

然而,不可忽视的是,2nm工艺的高能耗问题。在台积电的2nm工艺中,每小时的能耗高达20万度,这对于环境和生产成本提出了新的挑战。面对这些问题,台积电也在积极寻求解决方案,包括在新竹科学园区的Fab 20工厂建立2nm生产基地,并计划扩展到台中科学园区,通过多阶段工程逐步提升良率和降低能耗。

台积电2nm与3nm技术的关键区别不仅体现在晶体管架构的革新上,还包括了晶体管密度、功耗性能的显著提升以及新工艺的引入。这些进步不仅满足了市场对高性能及低功耗芯片的需求,也为未来半导体技术的发展指明了方向。尽管面临高能耗和成本上升等挑战,台积电通过科学的投资布局和技术创新,继续引领行业前行。未来几年,2nm技术必将成为推动芯片产业发展的重要动力,进一步巩固台积电在全球半导体市场中的龙头地位。

本文来自:什么值得买